吉林大學計算機系統結構 第三章 指令級并行 曲冠南老師版筆記

指令級并行(Instruction-Level Parallelism, ILP)是計算機系統結構中的重要概念,旨在通過同時執行多條指令以提高處理器性能。本章主要討論指令級并行的基本原理、實現技術和相關優化策略,基于曲冠南老師的教材和課程內容整理。

一、指令級并行的基本概念

指令級并行是指處理器在單個程序流中同時執行多條指令的能力。它依賴于指令之間的獨立性,通過流水線技術、超標量架構和動態調度等方法實現。ILP 的核心目標是減少指令執行的等待時間,提高處理器的吞吐率。

二、實現指令級并行的關鍵技術

1. 流水線技術(Pipelining)

流水線將指令執行過程劃分為多個階段(如取指、譯碼、執行、訪存、寫回),使不同指令在不同階段同時執行。流水線技術可以顯著提高指令吞吐率,但可能遇到數據相關、控制相關和結構相關等問題,需要通過冒險檢測和消除機制解決。

2. 超標量架構(Superscalar Architecture)

超標量處理器在每個時鐘周期內可以發射并執行多條指令。它通常包含多個功能單元(如整數單元、浮點單元),并通過硬件動態調度指令以利用并行性。超標量設計需要復雜的指令分發邏輯和資源管理。

3. 動態調度(Dynamic Scheduling)

動態調度通過硬件在運行時重新排序指令以避免相關性問題,常見技術包括 Tomasulo 算法。該算法使用保留站和公共數據總線來管理指令依賴,提高執行效率。

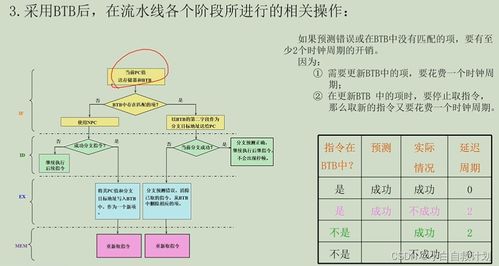

4. 分支預測(Branch Prediction)

分支預測技術通過預測程序分支的方向(如條件跳轉),減少控制相關帶來的流水線停頓。現代處理器采用復雜的預測器(如全局歷史分支預測器)以提高準確率。

5. 推測執行(Speculative Execution)

推測執行允許處理器在分支結果未確定前執行后續指令,若預測錯誤則回滾狀態。它結合分支預測和寄存器重命名技術,以最大化指令并行性。

三、指令級并行的局限性

盡管 ILP 能提升性能,但受限于以下因素:

- 數據相關:指令間的依賴關系限制了并行度。

- 控制相關:分支指令導致流水線停頓。

- 資源沖突:功能單元和寄存器的數量限制了同時執行的指令數。

- 功耗和復雜度:高 ILP 設計增加硬件復雜性和能耗。

四、優化策略

為提高 ILP,可采用以下方法:

- 編譯器優化:如循環展開、指令調度以減少相關性問題。

- 硬件支持:如多線程技術(同時多線程 SMT)以隱藏延遲。

- 高級架構:如 VLIW(超長指令字)由編譯器靜態調度指令。

指令級并行是現代處理器設計的核心,通過流水線、超標量和動態調度等技術實現性能提升。其有效性受限于指令依賴和硬件資源,需要結合軟硬件協同優化。曲冠南老師的課程強調了對這些概念的深入理解和實踐應用,為計算機系統服務提供了重要基礎。

如若轉載,請注明出處:http://www.xpjcar.cn/product/18.html

更新時間:2026-01-07 18:22:43